PRACTICA 2 DE DIGITALES

Objetivo: Comprobar que la utilización de los teoremas del algebra booleana ayudan a la simplificación de expresiones para optimizar el uso de componentes en su implementación.

Desarrollo:

1. Implementar las siguientes expresiones booleanas y obtener la tabla de verdad.

2. Simplifique las expresiones utilizando los teoremas e implemente la expresion resultante. Obtenga su tabla de verdad.

a) ABC' + (ABC')'

b) (AB + CD')(AB + D'E)

c) (AB + C)+ (D'E + F)' + (D'E +F)

d) A + B'C + D'(A + B'C)

e) AB'(C + D) + (C + D)'

f)[(EF)' + AB + C'D'](EF)

Resultados:

1.- Desarrollar en simulación las implementaciones y su comprobación

2.- Verificar que las implementaciones físicas tengan la misma tabla de verdad

3.- Analizar las consideraciones técnicas de la implementación como:

a)cargabilidad adecuada, tanto de entrada como de salida

b)Polarización, corriente, potencia utilizada en la implementación, etc de las compuertas utilizadas y porque.

c)que tipo de configuración interna de entrada y salida tiene las compuertas utilizadas.

4.- Escriba la conclusión de la práctica.

Desarrollo:

1. Implementar las siguientes expresiones booleanas y obtener la tabla de verdad.

2. Simplifique las expresiones utilizando los teoremas e implemente la expresion resultante. Obtenga su tabla de verdad.

a) ABC' + (ABC')'

b) (AB + CD')(AB + D'E)

c) (AB + C)+ (D'E + F)' + (D'E +F)

d) A + B'C + D'(A + B'C)

e) AB'(C + D) + (C + D)'

f)[(EF)' + AB + C'D'](EF)

Resultados:

1.- Desarrollar en simulación las implementaciones y su comprobación

2.- Verificar que las implementaciones físicas tengan la misma tabla de verdad

3.- Analizar las consideraciones técnicas de la implementación como:

a)cargabilidad adecuada, tanto de entrada como de salida

b)Polarización, corriente, potencia utilizada en la implementación, etc de las compuertas utilizadas y porque.

c)que tipo de configuración interna de entrada y salida tiene las compuertas utilizadas.

4.- Escriba la conclusión de la práctica.

1.- Desarrollar en simulación las implementaciones y su comprobación

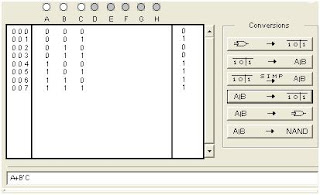

Se introdujo la función en multisim y se desplegaron los datos

a) ABC' + (ABC')'

La simplificación: es 1

A+A’=1

b) (AB + CD')(AB + D'E)

La simplificación: AB+ECD'

c) (AB + C)+ (D'E + F)' + (D'E +F)

La simplificación: AB+C+A'+A

d) A + B'C + D'(A + B'C)

La simplificacion: A+B'C

e) AB'(C + D) + (C + D)'

La simplificacion: AB'+C'D'

f)[(EF)' + AB + C'D'](EF)

La simplificacion:

2.- Verificar que las implementaciones físicas tengan la misma tabla de verdad

a) ABC' + (ABC')'

Utilizando compuertas

Led encendido

La simplificacion:1

b) (AB + CD')(AB + D'E)

Con compuertas

Led apagado Led encendido

La simplificacion: AB+ECD'

Compuertas

Led se apaga Led se enciende

En la siguiente imagen se muestra la función cuando el led esta apagado

c) (AB + C)+ (D'E + F)' + (D'E +F)

Compuertas

Led se apaga Led se enciende

La simplificacion: AB+C+A'+A

Compuertas :

Led se apaga Led se enciende

d) A + B'C + D'(A + B'C)

Y utilizando las compuertas queda como se observa a continuación

LED apagado LED encendido

La simplificación: F=A+B’C

Y utilizando las compuertas queda como se observa a continuación

Circuito con LED apagado Circuito con LED encendido

Como se muestra en la siguiente figura la posición del led en modo

A B C | B’C | F=A+B’C |

000 | 0 | 0 |

e) AB'(C + D) + (C + D)'

Diagrama simple

Y utilizando las compuertas queda como se observa a continuación

LED encendido LED apagado

La simplificación: F=AB’+C’D’

En la figura siguiente se observa el circuito implementando compuertas negadas, OR y AND.

Circuito con LED encendido Circuito con LED apagado

En la siguiente imagen se muestra la función cuando encendió el led

f) [(EF)' + AB + C'D'](EF)

Compuertas

Circuito con LED apagado Circuito con LED encendido

La simplificacion:

compuertas:

Circuito con LED apagado Circuito con LED encendido

3.- Analizar las consideraciones técnicas de la implementación como:

A- cargabilidad adecuada, tanto de entrada como de salida

FAN–IN AND FAN–OUT

Para el diseño con semicondutores los dispositivos TTL ,la entrada y salida de los parametros de carga de todas las familias y se normalizan de la siguiente manera

Se especifica como tener un factor de carga de entrada de 1 U.L. (También se llama un fan-in de una carga.)

La compuerta AND(SN74LS08) , OR(SN74LS32), INVERSOR (SN74LS04)

FAN-IN

IIL= -1.6m 1.6m /1.6m=1 UL

IIH= 40µ 40µ/40µ=1 UL

FAN-OUT

La salida de las compuertas TTL 74LS00 es :

Bajo (Low) IOL=16 mA Alto (HIGH) IOH=800 µA o .8m

IIL= 1.6m 16m/1.6m =10 UL (Low)

IIH= 40µ 800 µA/40µ =20 UL (High)

Factores de unidad para la familia TTL básicos

B- Polarización, corriente, potencia utilizada en la implementación, etc de las compuertas utilizadas y porque.

Esta familia se distingue por su bajo consumo de potencia (L=LOW POWER). Ello se consigue aumentando significativamente los valores de las resistencias de polarización con lo que se disminuye la corriente que circula por el sistema y con ello la potencia disipada. Si la potencia disipada en una puerta típica de la familia 54/74 es de 10 mW la de la puerta equivalente en la versión 54L/74L es de 1 mW.

El ahorro de potencia se paga con una pérdida en la velocidad: de los 10 nsg de tiempo de retardo típicos en la familia original se pasa a unos 33 nsg de retardo en esta familia

C- Que tipo de configuración interna de entrada y salida tiene las compuertas utilizadas.

CONFIGURACION DE LAS COMPUERTAS

AND (SN74LS08) A,B: son entradas Y : es salida

OR(SN74LS32)

INVERSOR (SN74LS04)

No hay comentarios:

Publicar un comentario